了解更多信息,请联系:

在当今日益高速发展的半导体行业中,数字验证已成为芯片设计不可或缺的核心环节。随着技术的不断进步,这一领域已经演变成为庞大的产业链中的关键组成部分。在智能驾驶、数据中心和人工智能等领域对高性能芯片需求的推动下,系统级芯片(SoC)的集成度和复杂性达到了前所未有的高度。相应的,验证工具也持续面临速度、效率、仿真和验证任务的复杂多样性挑战。

应对上述挑战,单点工具显然难以破局,需要从全局思维出发,打造可覆盖早期、中期和后期全流程验证需求的EDA验证平台。

上海合见工业软件集团有限公司(以下简称合见工软)经过持续的布局,在全方位筑实EDA数字验证全平台领域持续精进。合见工软验证产品市场总监曹梦侠在最近举办的ICCAD上“芯基建报告:全方位筑实EDA数字验证全平台”的演讲中提到,合见工软推出的EDA数字验证全平台,已覆盖了芯片验证全流程全场景需求,包括了从前期虚拟原型架构设计建模、早期及中期的模块级与子系统级功能验证仿真到中期子系统级至后期全系统级硬件加速仿真与原型验证。

硬件验证无法兼顾性能和效率

一般来说,数字芯片设计流程主要分为两路,一路是硬件和软件的功能验证,作用是确保芯片整体的功能正确性;另一路是数字实现,将RTL设计历经复杂的实现流程转换成Foundry可以生产的数据格式;这两路分别签核之后,送到Foundry去生产制造,最后流片再完成封装测试。

典型的SoC设计一般会采用外购IP(如CPU、互联总线、各种高低速接口、Memory等等)与自研IP相结合的方式,曹梦侠介绍,因而面临不同层级的验证需求。

曹梦侠解读说,对于自研的IP,其规模可能相对较小,这个层级的功能验证一般用仿真软件工具Simulation就可以做到。但对于子系统级到全系统级规模的功能验证,仿真软件会越跑越慢,甚至遇到仿真工具无法支撑的情况,在这种情况下需要硬件加速器Emulator的支持。此外,SoC不止包括底层的硬件,还包括上层的软件,而且系统越大软件验证体量越大。对于芯片上层软件的验证,如果对运行性能要求不高也许可以采用硬件仿真加速器跑,但以现如今的软件体量,大多对运行性能有要求,所以必须采用原型验证Prototyping。

此外在硬件功能验证之前,一些客户的设计并不是一上来所有的RTL代码都是准备好的,曹梦侠对此介绍,这时候可以将系统的一部分模块跑在硬件验证系统上,还有一部分可用虚拟平台跑虚拟模型,二者整合起来以混合验证的方式更早地开始验证和软件开发,从而缩短产品上市时间。

上述的各类硬件验证工具平台在运行性能、调试效率、使用便利性等功能上各有优缺点,总体而言,单一工具在几项必要的关键指标上很难同时兼顾。曹梦侠提到,数字验证是一项非常复杂的过程,要求既高效又功能完整,还要应对复杂多任务场景,之前的传统单一平台无法同时满足。为了完成项目,客户一般不得不采购多种不同的工具来组成一套完整流程,导致巨大的人力和时间成本投入,特别是平台间衔接移植的成本很高,从Emulation到Prototyping往往可能需要好几个月的时间。且设计一旦改动,迭代时间可能也会较长。

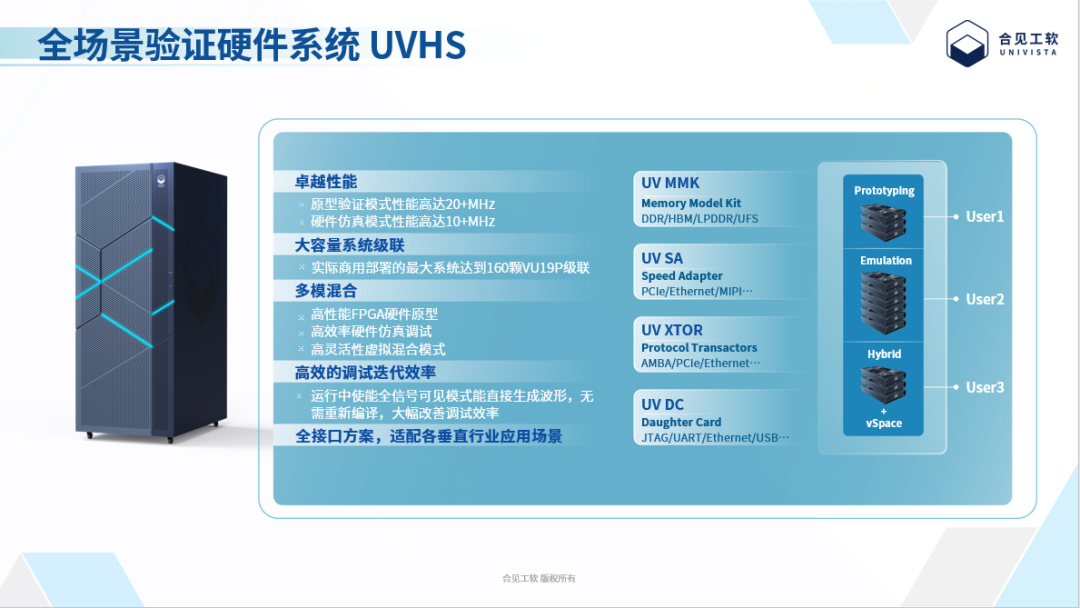

从本质上来说,这或是一个既要又要还要的问题。曹梦侠认为,在此情形下,理想的情况是将上述Emulation和Prototyping工具整合到一个单一平台之中合成统一流程,合见工软为此打造了全新商用级、高性能、全场景验证硬件系统UniVista Unified Verification Hardware System(UVHS)。

打造芯片级功能验证EDA平台

作为合见工软的重磅产品,高性能全场景验证平台UVHS在性能、容量、效率等层面实现了全面的“刷新”。

曹梦侠详细介绍说,一是卓越的性能:原型验证模式性能高达20+MHz,硬件仿真模式性能能达10+MHz多;二是可以实现稳定可靠的大容量级联系统,实际商用的单系统已达到160颗VU19P级联规模,约60亿逻辑门;三是多模混合,实现高性能FPGA硬件原型模式、高效率硬件仿真模式、高灵活性虚拟混合等功能;四是高效的调试迭代效率,运行中使能全信号可见模式能直接生成波形,无需重新编译,大幅改善调试效率;五是全面的接口方案,提供丰富的接口子卡、高速接口速率适配器、虚拟接口模型和存储模型,像已经大量商业部署的方案包括PCIe Gen5、Ethernet、MIPI、DDR5、HBM3等等,适配各种使用模式下的接口验证需求。

整体而言,UVHS可根据软硬件协同验证任务的不同,在不同性能要求、接口方案的使用模式和应用场景之间进行灵活切换,同时还能确保设计数据与环境的平滑移植,解决其他已有方案里切换模式的跨度大、难度高、效率低的难题,提升了验证效率和质量。

曹梦侠透露,目前该产品已在客户的主流大芯片项目中成功完成超过60亿门级设计规模的实际商业化部署,并实现成功流片迭代。

除在硬件验证工具层面实现整合之外,在软件仿真验证平台层面合见工软也在持续打磨。曹梦侠表示,合见工软的数字功能仿真器UniVista Simulator(UVS)在不断迭代,功能正确性及完备性已优先达到了Function Signoff级别;数字仿真调试器UniVista Debugger(UVD)着力提高验证调试效率,加速验证收敛,并可支持所有的验证工具;验证回归管理平台UniVista Verification Productivity System(VPS),持续致力于提升RTL回归效率。

值得一提的是,为打造从芯片到板级全覆盖的电子系统级虚拟原型解决方案,合见工软还推出了虚拟原型设计与仿真工具套件UniVista V-Builder/vSpace,包括系统级原型设计工具V-Builder和虚拟原型仿真环境vSpace。这一套件突破了传统的基于真实硬件的软件开发与测试限制,解决了软硬件解耦难题,并且在原型创建、编译与仿真性能方面更具优势。

曹梦侠指出,早期的软件开发可采用纯vSpace的使用场景;在UVHS Emulator与vSpace混合使用时,设计一部分以RTL形式放在Emulator上面,另一部分放在vSpace里面用SystemC的model,中间经由通道互联。一般是SoC的场景下某些IP不全或硬件资源有限的情况下会考虑。三是APS和vSpace混合使用,一般用于IP级的软件开发。

无疑,全场景验证硬件系统UVHS为合见工软多维演进的产品战略打下了坚实的基础。结合UniVista V-Builder/vSpace虚拟原型、数字仿真器、验证管理等产品的多路并进,合见工软已构筑了一个芯片级功能验证EDA全平台,凭借高性能、大容量以及灵活可扩展架构,全面确保验证的可预期性、效率提升以及多样化需求。

在验证领域破局向前之际,合见工软的多维演进路线也在层层推进。曹梦侠最后强调,合见工软的愿景是“联结物理和数字世界 成就创意到产品实现”,不止是验证平台,还立志打造更全面的国产EDA工具,在IP、系统级封装协同设计和PCB领域全面稳步发展,形成EDA+IP+Solution闭环生态加速产品演进迭代,构筑芯片与系统联动设计与产业生态。未来合见工软将脚踏实地,持续打磨产品,与业界同仁一起合作打造国内的“芯”基建,助力解决卡脖子难题。

关于合见工软

上海合见工业软件集团有限公司(简称“合见工软”)作为自主创新的高性能工业软件及解决方案提供商,以EDA(电子设计自动化,Electronic Design Automation)领域为首先突破方向,致力于帮助半导体芯片企业解决在创新与发展过程中所面临的严峻挑战和关键问题,并成为他们值得信赖的合作伙伴。

了解更多详情,请访问www.univista-isg.com。