了解更多信息,请联系:

近年以来,生成式人工智能(AIGC)的爆发,以及智能手机、自动驾驶、物联网等“万物智能”的快速发展极大地推动用户追求更高性能的芯片,然而随着摩尔定律接近物理极限,SoC的器件微缩也明显放慢了脚步,而更先进、更复杂的工艺节点成本却持续稳步上升,越来越难以负荷。为此,通过先进封装技术提升芯片整体性能已成为半导体行业技术发展的重要方向,系统级封装、2.5D/3D IC、Chiplet等先进封装技术成为近年来备受瞩目的领域。

在这种趋势下,传统的芯片设计流程显然已经无法胜任,行业需要全新的EDA工具解决方案。在近日举办的ICCAD 2023“先进封装与测试(二)”分论坛上,上海合见工业软件集团有限公司(以下简称合见工软)技术支持总监李方分享了题为《系统级封装协同设计和互连技术》的演讲,阐述了合见工软在先进封装领域的布局。

先进封装设计的挑战

Yole数据显示,先进封装市场今年第三季度迎来23.8%的强劲增长,预计全年市场保持平稳增长,并在未来五年实现8.7%的年复合增长速度,从2022年的439亿美元增长至2028年的724亿美元。

先进封装带来的收益显而易见。李方指出,这些利好包括:

- 第一,支持普通MCM架构,可选择不同的工艺节点,尤其对部分企业而言,在一定程度上降低了先进工艺管制的影响。

- 第二,IP/Chiplet设计可复用,有效提升了可靠性,缩短开发周期,同时可缓解先进工艺产能不足导致产品上市时间延后的问题。

- 第三,合理降低先进工艺芯片的尺寸,采用低成本成熟制程,提升了可靠性和良率,有效降低制造成本。

- 第四,设计组合灵活多样,可满足不同的市场需求。

与此同时,先进封装所面临的挑战也是巨大的,包括Die to Die之间的互连关系复杂;MCM架构设计之间的纵向连接正确性无法保证;供电系统设计难度很高;D2D之间的高速接口定义受限,如果采用并列接口,走线资源要求高,传输距离短,而如果采用串行接口,同功耗下总带宽容易侵占IO区域,虽然UCIe等国内外标准开始定义互连芯粒之间接口标准,但尚不完善。除此之外,在互连模块的面积、延时和功耗,信号完整性、寄生参数抽取,以及散热、应力问题等方面也存在不小的挑战。

以一款AI芯片的架构为例,它通常包含ASIC芯片,多颗HBM,部分信号通过Interposer中介层进行横向互连,部分信号纵向连通到Package(封装),设计流程中所涉及的设计需要使用不同类型、不同供应商的EDA工具。例如ASIC设计采用IC后端的设计工具;HBM可能通过IP设计或其他设计格式;Interposer层则选择IC后端设计或封装设计工具;Package通常采用封装设计工具等等。

因而2.5D/3D先进封装时代,在设计时需要考虑从芯片到硅基板,从硅基板到封装基板、从封装基板到PCB的所有互连,如此多的层次节点互连存在很多设计难点,除了散热、信号完整性和电源完整性等基本挑战外,对EDA工具也带来了更为“碎片化”的挑战,需要一款系统级协同设计工具,来对所有涉及到的相关设计进行全面分析,并确保设计与设计之间相关互连等信息的正确性。

系统级协同设计EDA工具的挑战

不难看出,随着异构集成时代的到来,协同设计与集成开发被寄以重望,成为先进封装设计的主流趋势,而传统的系统级协同设计工具已然不适用于当下的需求,并面临着诸多局限性。

李方总结指出,首先,在传统系统级设计互连Sign-Off(签核)之前,为确保物理连接的正确性,通常采用工具从不同的设计文件中提取网络名(Net Name)信息,然后对设计之间的Net Name进行基于命名的查找比对,带来不小的隐患。

传统的先进封装设计基本用Excel来实现,虽然ASIC、HBM、Interposer等设计信息都能从表中导出来,但是有的表上只有Net Name,有的表上只有坐标信息,且表与表之间没有逻辑关系,无法得出准确有效的检查结果。先进封装一定要解决所有层级设计之间的互连的正确性验证,而传统方法只能解决管脚命名一致性检查这一问题,且存在一定的局限性,包括其他的必要检查无法快速准确实现或只能部分实现,无法直观快速定位出错信息的位置;多维度系统级垂直方向的互连正确性检查只能部分实现且普遍耗时较长,通常传统方式只能实现两个层级之间的检查;所有信号全链路通断检查只能部分实现,需要两天甚至更长时间,还只能检查一些比较关键的信号;无法覆盖到所有的外延信号,所有管脚缺失互连检查只能部分实现且耗时较长,通常需要两天以上甚至不能完成。

其次,跨多个设计领域,缺乏统一直观的设计页面,无法将不同格式、不同单位精度的设计数据放在同一个界面进行比对和查看,导致设计数据的导入不完整,并且很难将不同的设计数据进行高效的整理和操作。

此外,随着设计堆叠形式多样化,对支持2.5D/3D设计的功能需求增加,芯片数目不断增多,导致设计集成度越来越高,随着设计规模越来越大,所需要检查的信息越来越多,所要检查的项目也越来越详细,构建准确的逻辑连接关系困难,很难进行系统级检查。普通设计工具无法保证整个链路的节点互连是正确的,从而使得传统检查方式效率非常低下,而且容易出错。

另外,还有一些在先进封装设计环节中,单纯依靠传统方法没办法解决的问题,比如所有设计同时显示在一个界面快速建立设计互连逻辑;如何建立设计与设计之间的逻辑连接;生产数据与设计数据比对检查;封装设计中die的数据与ASIC的GDS数据的比对;一对多Pin基于面积的互连Net Mapping;Power&Ground的电源拓扑,如何实现系统级电源的拓扑检查以及Power&Ground网络管脚数量及信号数量配比等等。

因此,随着先进封装的迅速发展,传统设计方法已无法满足产业发展的需要,继续使用传统设计工具难以控制设计错误和设计风险,需要更高效、直观、简洁的系统级协同设计工具来解决这些挑战。

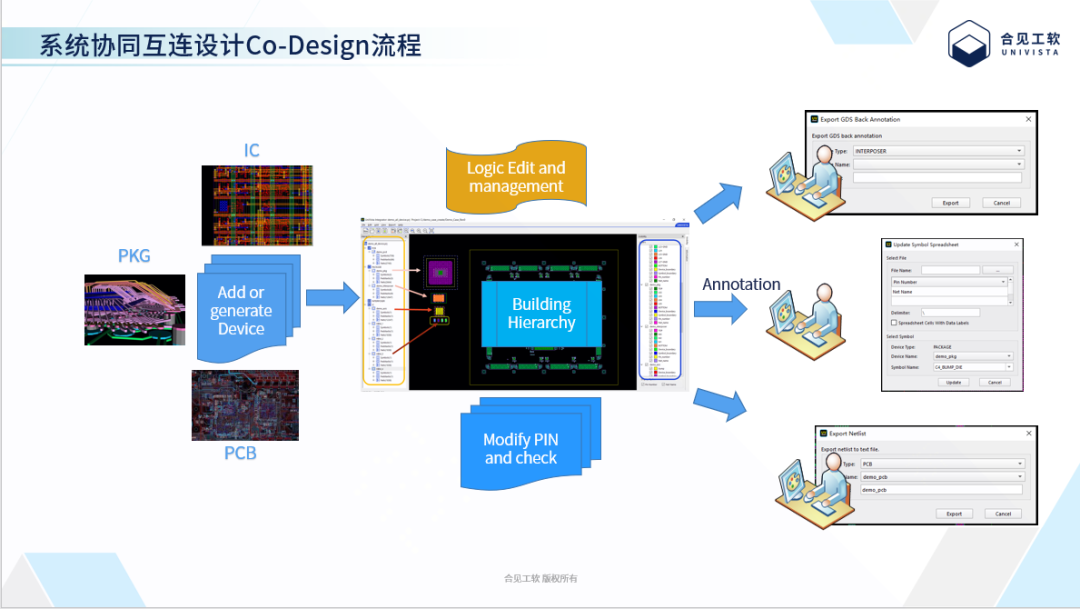

全面革新的UVI破解先进封装挑战

面对日益增长的市场需求,为高效解决2.5D、3D、SiP等各种先进封装系统级协同设计环境,作为高性能工业软件及解决方案提供商,合见工软发布了先进封装系统级设计协同Sign-off工具UniVista Integrator(简称“UVI”)。它能够支持在同一个设计环境中导入各种格式的IC、Interposer、Package、PCB数据,同时支持设计数据的协同设计。基于物理、图形、数据等信息,UVI能够根据不同应用设计,自动产生系统级互连关系网表,互连错误信息,网络断开类型,互连叠层信息等关键报告。合见工软的UVI产品可以帮助各领域的工程师能简单高效的修改优化设计,大大提高产品设计的一次成功率。

李方介绍,UVI的核心竞争力在于:

- 同一个设计界面集成多种相关设计数据,不同设计阶段的工程师能有效、直观地交流;

- 高效达成系统设计优化IO、Bump、Ball Map设计与优化;

- 检查设计之间的容错性、互连管脚之间的形状尺寸一致性;

- 系统级Net的短路及开路检查;

- 支持智能系统级设计互连即垂直方向的检查(系统级LVS)。

相比传统设计方案,UVI能高效灵活地帮助设计工程师简化设计流程、提升工作效率、提高设计质量、精准定位设计错误,并覆盖所有节点和网络的检查。使用UVI导入PCB、PKG、Interposer、IC等设计数据,可以在一个窗口就准确、直观地看到所有相关的设计数据,选择有匹配关系的Symbol进行匹配及物理位置、物理层的对齐,就完成了整个设计的关联。

UVI支持基于系统级的Ball Mapping设计及优化,可对Net灵活管理和灵活应用,对IP Bump灵活调整,以及对不规则Pin阵列快速检查,轻松实现对BallMap的网络名编辑,批量操作,批量处理;对Map阵列的自定义编辑,例如对自研IP Mapping的设计评估与规划,删减、增加、移动;对不规则Ball阵列的快速检查;Contact Device相互Sync net等等。

值得一提的是,UVI采用了业界特有的系统级网络连接检查技术,大幅提高了大规模2.5D/3D、先进封装的设计效率,并能完成人工难以实现的多层、多形式的复杂堆叠设计,可一键生成系统级网表,支持系统设计中任意两个Symbol之间通过指定Device建立通路,产生Net Mapping的关系。

在纵向的System Level LVS检查设置方面,UVI支持检查报告设置,具备高效严谨的系统级检查应用,而且有多达9项检查项目,涉及Net mapping、Unmapping Pin、Interface Pin、Geometry Difference、Tolerance Distance、Contact Layer、Golden Validate等,每一项都是系统级互连检查中不可或缺的环节,可将设计间互连检查时间由数天缩短至数小时,并且直观高效定位设计问题位置。

最后,李方总结,UVI软件工具支持主流Windows和Linux平台,设计操作灵活简单,具有高效全面的Sign-Off必备协同检查功能,并具备丰富的扩展应用,且性能优越:在Mapping计算性能方面,100万Pin的Mapping计算Position模式仅需8秒,Area模式仅需10秒;在显示性能方面,100万Pin设计全开,缩放,移动不卡顿,电脑核显支持,以及全圆显示卡顿,提升至使用电脑核显不卡顿。

关于合见工软

上海合见工业软件集团有限公司(简称“合见工软”)作为自主创新的高性能工业软件及解决方案提供商,以EDA(电子设计自动化,Electronic Design Automation)领域为首先突破方向,致力于帮助半导体芯片企业解决在创新与发展过程中所面临的严峻挑战和关键问题,并成为他们值得信赖的合作伙伴。

了解更多详情,请访问www.univista-isg.com。